# Nanoscale Systems for Optical Quantum Technologies

Grant Agreement No: 712721

Start Date: 1st October 2016 - Duration: 36 months

# D1.5 Laser and cavity control systems

**Deliverable:** D1.5

Work package: WP1 Nanomaterials, optical micro-cavities and

experiment control systems

**Task:** 1.4 Digital laser/cavity control system

**Lead beneficiary:** KEY

Type: Report

**Dissemination level:** Confidential

**Due date:** 30 September 2018

**Actual submission**

date:

29 September 2017

Author(s): Nestor Oliverio (KEY), Eneas Puertas (KEY), David

Hunger (KIT), Julia Benedikter (KIT)

### **Version history**

| Version | Date       | Author(s)             | Description                |

|---------|------------|-----------------------|----------------------------|

| V1      | 24/09/2018 | D. Hunger(KIT)        | First draft, KIT part      |

| V3      | 19/12/2018 | Eneas Puertas (KEY)   | KEY part, consolidation    |

| V4      | 20/12/2018 | Nestor Oliverio (KEY) | Review                     |

| V5      | 21/12/2018 | Eneas Puertas (KEY)   | Consolidation, final draft |

| V6      | 29/12/2018 | Eneas Puertas (KEY)   | Final submitted version    |

## **Copyright Notice**

Copyright © 2018 NanOQTech Consortium Partners. All rights reserved. NanOQTech is a Horizon 2020 Project supported by the European Union under grant agreement no. 712721. For more information on the project, its partners, and contributors please see http://www.nanoqtech.eu/. You are permitted to copy and distribute verbatim copies of this document, containing this copyright notice, but modifying this document is not allowed.

#### **Disclaimer**

The information in this document is provided as is and no guarantee or warranty is given that the information is fit for any particular purpose. The user thereof uses the information at its sole risk and liability.

The document reflects only the authors' views and the Community is not liable for any use that may be made of the information contained therein.

# **Table of Contents**

| Deliverable Description                                                                                                                                                                                            | 4           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Hybrid cavity control system                                                                                                                                                                                       | 4<br>4<br>4 |

| Implementation of a fully digital cavity stabilization  PID implementation and validation  Analog to digital transition (PID)  Digital filter implementation and validation  Analog to digital transition (Filter) | <br>9       |

| System validation                                                                                                                                                                                                  | 12          |

| Conclusion                                                                                                                                                                                                         | 14          |

| References                                                                                                                                                                                                         | 15          |

# **Deliverable Description**

This deliverable reports the work done by KEY and KIT to develop control systems for tunable optical microcavities and for laser frequency stabilization.

# **Hybrid cavity control system**

As an intermediary step, we have implemented a cavity control system that combines analog circuits and software-based, digital feedback to stabilize and scan a tunable microcavity in a cryogenic environment. The different objectives for the control system are

- small-scale ( $\sim 30x30~\mu m$ ) lateral scanning of the cavity to perform scanning cavity microscopy for identification of suitable nanocrystals for cavity coupling

- large-scale (up to mm) positioning to access different areas on the mirror, to compensate thermal contraction upon cool down, and to operate the cavity at different lengths

- stabilization of the mirror separation to maintain resonance conditions (~pm).

### Mechanical and thermal setup

Lateral scanning is realized by a home-built, piezo-based nanopositioning mechanics, which is described in more detail in D1.1. For large-scale tuning, electro motors and a gearing mechanism together with fine-threaded screws are used. Several refinements have been necessary to make this setup fully cryo-compatible after the first proof-of-principle demonstration described in D1.1. E.g. the piezos and the motors need to be operated at elevated temperatures, requiring the design and implementation of suitable

thermal spacing and radiation shields. Also, the thermal contact of the sample to the cold finger of the cryostat needed to be optimized to ensure sufficiently low sample temperature, while at the same time minimizing mechanical contact, since the cold platform displays significant mechanical noise that extends to high frequency. Therefore, a flexible thermal link was implemented, and a passive mechanical isolation stage based on Teflon spacer sheets was incorporated to suppress the transmission of high frequency mechanical noise to the cavity. With this system, scanning cavity microscopy and partial stabilization is now possible also under cryogenic conditions (see below). Figure 1 shows an example of scattering loss of individual Eu<sup>3+</sup>:Y<sub>2</sub>O<sub>3</sub> nanocrystals observed at 9K from a cavity transmission measurement as used for the identification of suitable crystals.

Fig. 1 Scanning cavity microscopy at cryogenic temperature of individual nanocrystals. The length scale is not calibrated, the image size is estimated to be  $10x10\mu m^2$ .

#### **Control system and cavity stabilization**

The motors and piezos are driven by amplified analog outputs of a computer card, which itself is controlled by a python-based experiment control program. To achieve optimized cavity stabilization in the noisy environment of the cryostat, we have combined an analog

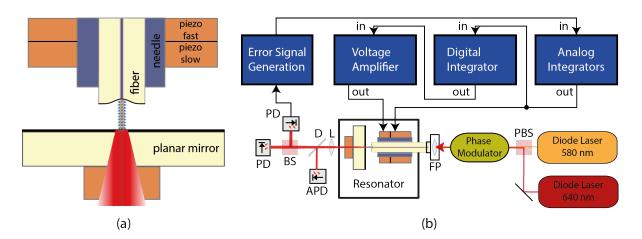

Fig. 2 a) Schematic drawing of the tunable cavity: The fiber is attached to a fast and a slow piezo for length stabilization (+2 piezos for lateral scanning). The planar mirror is movable via electro motors. b) Schematic drawing of the opto-electronic setup for cavity length stabilization. Phase modulated light transmitted through the cavity is used for error signal generation, the analog integrators provide fast feedback, digital feedback enables long-term drift compensation.

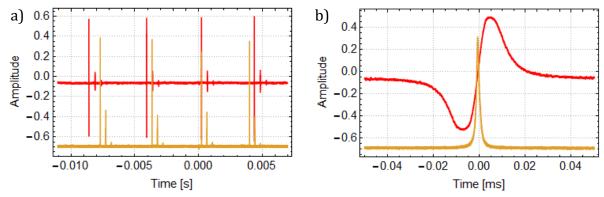

PI controller with tunable transfer function and a digital feedback for drift compensation. This is a modification and extension of an earlier scheme described in [Brachmann16]. Figure 2 shows the schematic setup. Using a PDH error signal generated from a stabilization laser at 640 nm (see D1.1 for more details), we could achieve stable locking also during operation of the cryostat. Figure 3 shows the achievement of double-resonance conditions for 580 nm and 640 nm by tuning the cavity over several longitudinal resonances, as required for active stabilization during resonant spectroscopy experiments. The finesse of the cavity amounts to 13000 – 20000 at 580 nm (depending on the particular mirror pair used in the experiment), while it is about 1500 at 640 nm, chosen to increase the capture range of the lock.

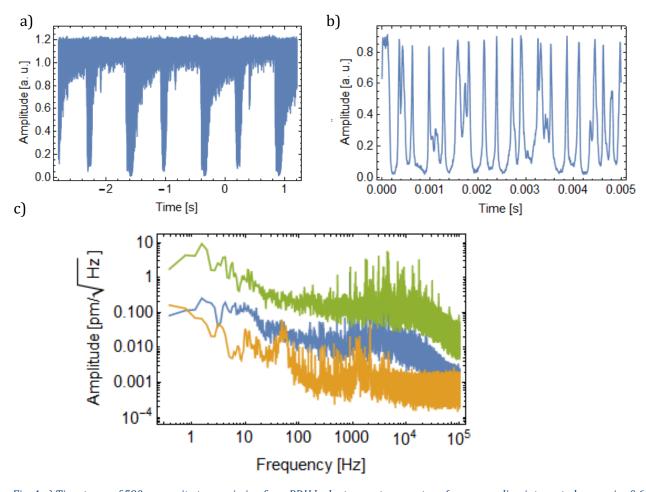

The achieved noise performance is shown in Figure 4. For calibrated noise spectroscopy, we stabilize the cavity at the side of a resonance such that mechanical noise translates into intensity noise in an approximately linear manner. To observe the stability of the transmitted signal, and for future spectroscopy, we employ a Pound Drever Hall (PDH) stabilization at the maximum of a resonance. With the cryostat off, the integrated mechanical noise amounts to 0.6 pm, limited by the detector noise at large frequencies. For a running cryostat with the setup still close to room temperature, the noise level increases to 4 pm, and remains locked during the entire cycle of the closed cycle cooler. These values are close to those reported for the earlier system described in D1.1, however

Fig. 3 a) Cavity length tuning (here shown as a function of piezo scan time), showing simultaneous resonance for 580 nm (orange) and 640 nm (red) lasers at one particular longitudinal mode pair. b) Zoom into the transmission resonance of 580 nm light (orange) and the error signal of the 640nm stabilization laser (red) for double resonance conditions.

with the difference that now, the system is fully functional (including all piezos, motors, wires required for lateral scanning, and thermalization). In particular, the thermalization link initially introduced significant additional noise, which could be reduced by an improved design. The thermalization now also allows us to cool down the sample to a temperature of 8 K in the best case, and to 12 K for data shown in Fig. 4a,b,c. Surprisingly, at low sample temperature, we observe a significant increase in mechanical noise by more than a factor 10. The integrated noise level is then 60 pm, which is already larger than the cavity linewidth of ~15 pm, as can be seen also in the time trace of Figure 4b. A large fraction of this additional noise is at high frequencies, up to 50 kHz, which cannot be suppressed even by an advanced cavity lock. This additional noise has so far inhibited further spectroscopy experiments. We currently redesign the mechanical isolation stage and thermal link to better suppress passively the transmission of high frequencies. In parallel, we also develop mechanical cavity platforms where all tuning degrees of freedom can be eliminated after initial alignment for improved passive stability under operation within the cryostat. Also, we prepare the purchase of a flow cryostat with significantly lower vibration levels, where the stability of the current cavity platform is expected to be high enough for operating also cavities with higher finesse, up to 100000.

Fig. 4 a) Time trace of 580 nm cavity transmission for a PDH lock at room temperature (corresponding integrated rms noise 0.6 pm). Periodic noise peaks synchronous with the closed-cycle cooler are apparent, while the lock is maintained over the entire period. b) Time trace of 580 nm light for a PDH lock at 12 K (60 pm). c) Noise spectra for side of fringe lock with cryostat switched off (orange), with cryostat running and sample at >200 K (blue), with cryostat running and sample at 12 K (green).

# Implementation of a fully digital cavity stabilization

### PID implementation and validation

Having a fully digital cavity stabilization system will benefit from the flexibility and the higher levels of customization it offers, to improve performance and stability of the system. It won't be necessary to swap digital components to change a filter or reconfigure the stabilization controller, just generating a new digital configuration file or simply updating the pre-existing parameters of the system (in a matter of seconds to be applied).

The first step into a fully digital environment, is to have a digital PID controller available to be used in M3602A FPGA programming platform, initially as an external IP but later as a built-in IP in the library block.

The IP has been developed using Xilinx's Vivado FDK (FPGA development kit) and it consists of 3 Digital Signal Processing blocks (DSP from now on) being used as the P, I and D components plus some extra logic to have the extra capability of slowing the sampling rate of the IP (as some times due to the latency of the feedback system is not required to go full speed).

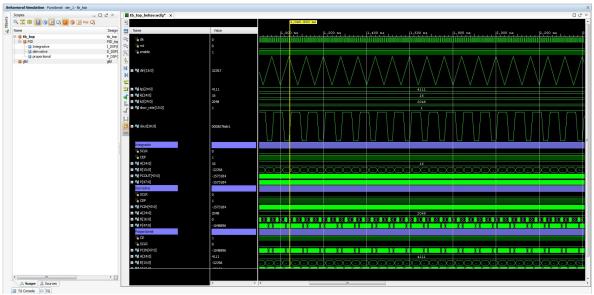

To validate that the theoretical implementation was correct, the design was simulated using the built-in simulator in Vivado.

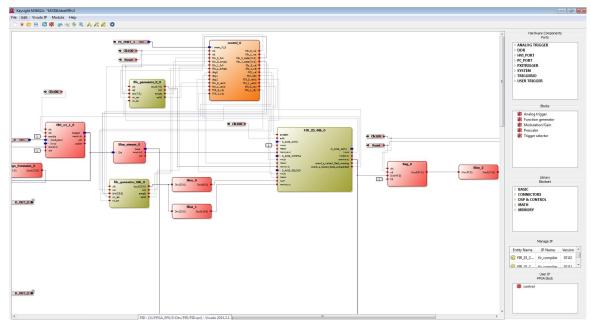

Fig. 5 Vivado built-in simulator

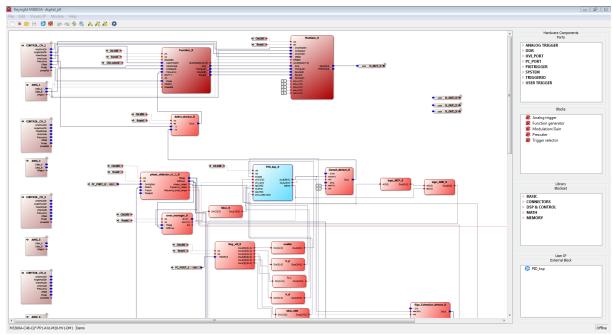

Once simulated, the block was used to implement a Digital Phase Lock Loop (PLL) using M3602A platform and a M3300A module. This test leveraged the in/out capabilities of the module as well as the external SW-enabled control of the custom logic inside the reconfigurable region of the FPGA.

Fig. 6 M3602A test implementation

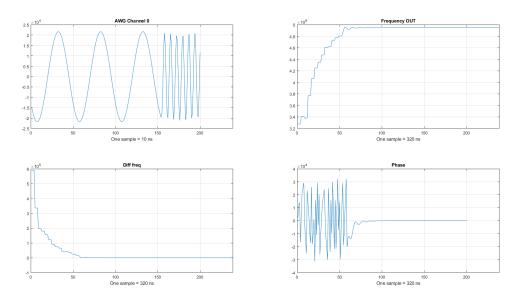

The results of the test showed that the IP performed as expected, being able to lock to any given frequency + phase within the system's range ( $[0, f_s/2]$  [-180 $^{\circ}$ ,180 $^{\circ}$ ]).

Fig. 7 PLL test results

# **Analog to digital transition (PID)**

To effectively transition from the analog PI box to the digital PID, the parameters for the digital counterpart should be obtained either by characterizing the actual configuration of the PI box or by a "by-hand" adjustment.

The first method requires the injection of a step signal into the PI box and the calculation of the inverse step response using MATLAB and the output signal. This provides the

system's parameters (P,I and D constants) which will be used as starting point for the PID configuration.

The second method, more experimental, requires a better knowledge of how the different parameters affect the behaviour of the PID block. Without going too much into details:

The Proportional constant  $(K_p, P_{out} = K_p \cdot e(t))$  adds a certain gain to the error input. A big value can cause instability issues but a small one can produce a less responsive/sensitive controller.

The Integrative constant  $(K_i, I_{out} = \int_0^t e(\tau) d\tau)$  provides a correction proportional to the error and the duration of it. This constant provides protection against the steady state error that comes with a pure proportional controller. As it considers all previous values, this part of the controller is susceptible to overshoot thus being able to cause the controller to be unstable.

The Derivative constant  $(K_d, D_{out} = K_d \cdot \frac{de(t)}{dt})$  acts as a low pass filter that eliminates high frequency components from the error signal, limiting high-frequency gain and noise. This component "predicts" the system behaviour, improving settling time and stability which allows to increase P and I constants to improve noise/disturbance cancelations and response time.

A safe approach using this method will be to first increase  $K_p$  and  $K_i$  until the system exhibits overshoot and from that point adding  $K_d$  to the equation trying to minimize the effects of the integrative constant (gaining stability) and decreasing the locking time. As  $K_d$  is added,  $K_p$  and  $K_i$  can be increased to improve response and performance.

### Digital filter implementation and validation

In addition to the substitution of the analogue PI box by a fully digital PID controller, some analogue filters were susceptible of being substituted by digital counterparts.

Using digital filtering provides the advantage of being able to reconfigure the filter's frequency response without having to physically change the test setup. Instead of swapping analogue filters, the user only needs to re-calculate the filter's coefficients for the new frequency response (using MATLAB or any other similar tool) and update the digital filter with the new sets through the software interface (using python, C or any other of the supported languages). This is a huge advantage, since analog filters are extremely difficult to tune, so digital filters allow a much better tuning and optimization of the control loop.

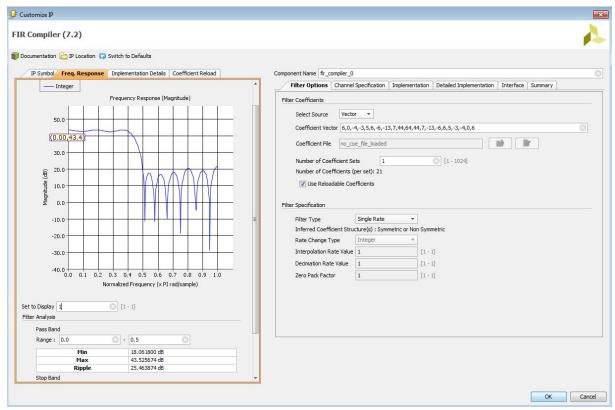

To leverage the IP catalogue that Xilinx provides, the first implementation of a filter was done using Vivado's IP generator, specifically the FIR generator.

Fig. 8 Vivado FIR compiler tool

With the "Use Reloadable Coefficients" checked, we can easily update the coefficients using the software-based user interfaces available in M3602A. This allows for fast reconfiguration without having to regenerate again the whole system. These interfaces can be used though the supported programming languages (C, C#, C++, Python). In addition, when setting the default coefficients, the tool provides a graph with the expected frequency spectrum response.

Once the IP was created, it was easy to validate using M3602A FDK.

Fig. 9 M3602A FIR filter validation project

The only limiting factor when implementing a filter on a FPGA based system are the available resources, more specifically the number of DSP the user has access to. In the specific case of an M3300A module with a Kintex 7 K410 FPGA, the available DSP number is around 550 DSPs which would translate into a 550 taps FIR filter.

If the available number is not enough for the required FIR filter, the tool provides an option to work with sampling rates lower than the main frequency the filter works at (e.g. sampling a signal at 20 MHz while the filter works at 100 MHz). This reduces the number of DSPs required by the filter, as it can use a just one for several taps.

#### **Analog to digital transition (Filter)**

One of the most important aspects to mimic the behaviour of an analog filter is its frequency response. If this aspect can be replicated with a digital filter, its behaviour can be guaranteed to be equal. In digital filter design, the value of the different coefficients that are used in the filter's taps determine the frequency response of it.

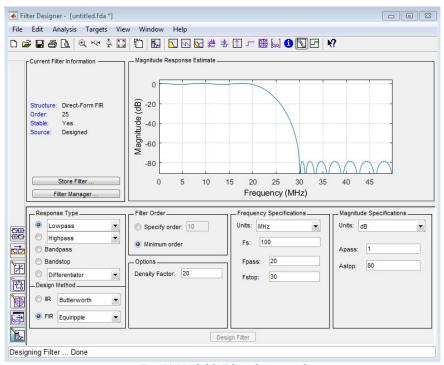

There are many filter design tools, we choose MATLAB as it provides a good environment that produces not only the coefficients required to fulfil the performance required but also generates several graphs that provide a quicker way to assert if the behaviour and performance of the filter will meet the expectations/requirements.

Fig. 10 Matlab's Filter design tool

As MATLAB generates the parameters on a decimal notation, they must be converted into integers for the digital filter to be able to use them effectively.

# **System validation**

The first element that has been validated in the lab has been the digital PID controller.

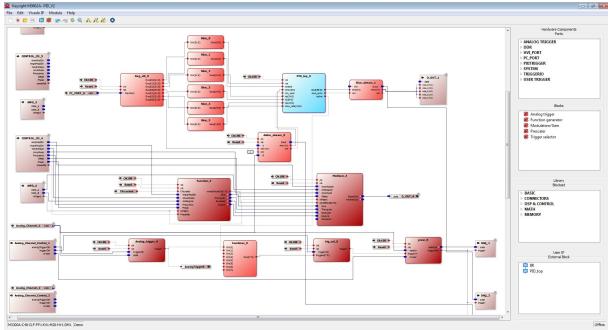

To do that, the default M3602A project for the M3300A module was stripped of all non-required blocks. Then, the digital PID and some extra blocks to control the DC offset where added.

Fig. 11 Feedback control logic M3602A project

To control the DC offset and the different parameters of the PID IP as well as to capture the error signal before and after the DC offset is applied and the correction signal coming out of the PID block, a GUI was developed using python.

Fig. 12 Python-based GUI

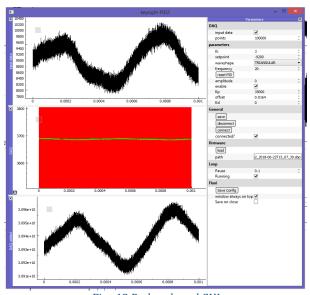

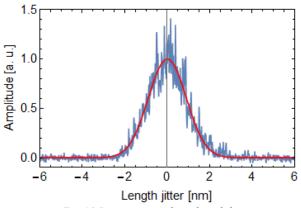

The digital PID was tuned to offer a similar performance to its analog counterpart. To characterize the lock performance, the rms length jitter of the resonator was first characterised without active stabilization (cavity setup in the cryostat at room temperature).

Integrating over the position of a cavity resonance for over 2 min yields the following length jitter distribution:

Fig. 13 Passive cavity length stability

A Gaussian fit gives a standard deviation of 890 pm. The intrinsic cavity resonance has a linewidth of 20 pm.

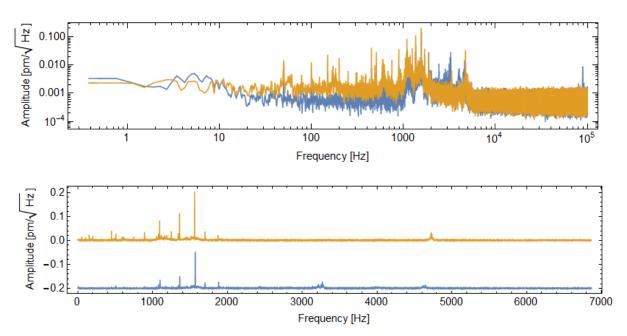

Fig. 14 Amplitude spectral density of cavity length fluctuations with the digital (orange) and the analog (blue) PI control.

Top: Logarithmic scale. Bottom: Linear amplitude scale, blue spectrum displaced by -0.2 for clarity.

After measuring the jitter without any stabilization whatsoever, it was measured again in two scenarios:

- Analog PI box + Analog low pass filter (3dB point at 2kHz)

- Digital PID + Analog low pass filter (3dB point at 2kHz)

With the analog PI, the obtained rms length jitter for the resonator was 0.4 pm. Then, after calibrating the digital PID to perform in line with what was observed from the Analog PI box, the rms length jitter obtained was 0.6 pm. The results are very similar which prooves that the digital PID can replace the analog implementation with a very basic tuning. It is expected that improvements in the tuning and PID implementation will improve the performance, more on this is commented in the conclusions.

The second element to be validated was the FIR filter. This element is intended to deal with resonance frequencies of the mechanical system. It is important to note that a low pass filter is the simplest and more robust implementation for an analog implementation. Notch filters or other techniques can be used in the digital domain but are quite hard to implement successfully with analog circuits.

To avoid implementation problem due to high utilization side effects, the FIR filter was limited to 400 taps (80% of the available DSP blocks). When designing the filter to work at a rate of 100 MSPS (Mega Samples Per Second = 1.000.000 samples/s) we discovered that the implementation of a low pass filter with a 3 dB point at 2 kHz having a Fs of 100 MHz was not possible with the available taps we had for our filter, being the required number of taps many orders of magnitude above the maximum value we could have.

The next approach we tried was to lower the effective sampling rate of the error signal to a much smaller one that could allow a more efficient use of the available number of DSPs (by benefiting from the coefficient multiplexing inside the filter). We used a custom IP to lower the sampling rate from 100 MHz to 100 kHz which was way above the 2 kHz lowpass frequency the filter was going to work at. With this approach we were successfully able to implement a low pass filter with the required specifications using only about 10% of the available DSPs, but the latency is still a big problem. The final filter delay was of about hundreds of microseconds. As the effect of the correction generated by the PID on the system is almost immediate, this amount of delay would cause the system to be most likely unstable.

The only alternative we have is to implement an IIR filter (Infinite Impulse Response). IIR filters benefits of significantly better roll-off compared to FIR filters with a smaller number of coefficients, but they suffer from a much higher complexity and a tendency to be unstable due to their recursive nature (the use of previous samples as feedback affects stability).

We did a rough design of an IIR filter with a sampling frequency of 100 MHz and a cutoff frequency of 2 kHz and it only required 56 DSPs with a latency of 560 ns which is very good for the time constant of the mechanical system

### Conclusion

We have implemented and improved a home-built cryogenic cavity platform together with a digital-based feedback control loop. Replacing the analog implementation by a digital one is a key step that going forward will provide total flexibility to optimize the feedback algorithms to further improve the cavity stability. Further improvements on mechanical isolation and thermalization are still required to achieve stable operation for cryogenic spectroscopy.

After matching the performance of the analog PI box, a more in-depth calibration of the PID block, which is currently not using the Kd constant, will lead to an improved performance of the control loop. In addition, the IIR filter will round the all-digital transition, providing a quite flexible environment.

Once these improvements are completed, further actions will be discussed to increase the cryogenic cavity capabilities and control loop performance. The full digital implementation will allow to implement techniques not imaginable or very difficult to implement or tune in the analog domain, like for instance adaptable notch filters fully matched to the mechanical response of the cavity and its variations, feed-forward techniques, etc...

## References

J. F. S. Brachmann, H. Kaupp, T. W. Hänsch, D. Hunger, Photothermal effects in ultraprecisely stabilized tunable microcavities, Optics Express 24, 21205 (2016).